# S2-Compatible 7-Input 3-Output Audio/Video Switch

### **Description**

The CXA2069Q is a 7-input, 3-output audio/video switch featuring I<sup>2</sup>C bus compatibility for TVs. This IC has input pins that are compatible with S2 protocol.

#### **Features**

- 4 inputs that are compatible with S2 protocol

- Serial control with I2C bus

- 7 inputs, 3 outputs

- The desired inputs can be selected independently for each of the 3 outputs

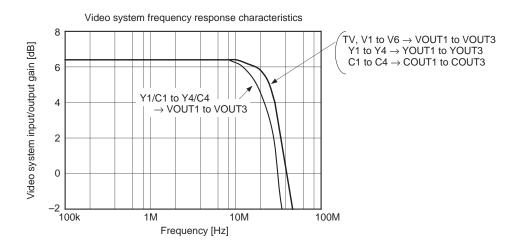

- Wide band video amplifier (20 MHz, -3 dB)

- Y/C MIX circuit

- Slave address can be changed (90H/92H)

- · Audio muting from external pin

- High impedance maintained by I<sup>2</sup>C bus lines (SDA, SCL) even when power is OFF

- Wide audio dynamic range (3 Vrms typ.)

#### **Applications**

Audio/video switch featuring I<sup>2</sup>C bus compatibility for TVs

#### **Structure**

Bipolar silicon monolithic IC

| Absolute Maximu                     | ım Ratings  | (Ta=25 °C)  |    |

|-------------------------------------|-------------|-------------|----|

| <ul> <li>Supply voltage</li> </ul>  | Vcc         | 12          | V  |

| <ul> <li>Operating tempe</li> </ul> | rature      |             |    |

|                                     | Topr        | -20 to +75  | ℃  |

| <ul> <li>Storage tempera</li> </ul> | ture        |             |    |

|                                     | Tstg        | -65 to +150 | ℃  |

| <ul> <li>Allowable power</li> </ul> | dissipation |             |    |

|                                     | Po          | 1300        | mW |

|                                     |             |             |    |

Operating Conditions

Supply voltage 9±0.5 V

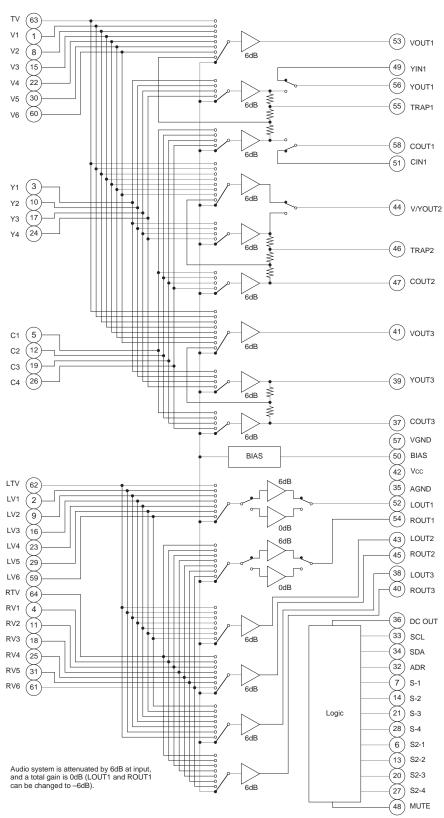

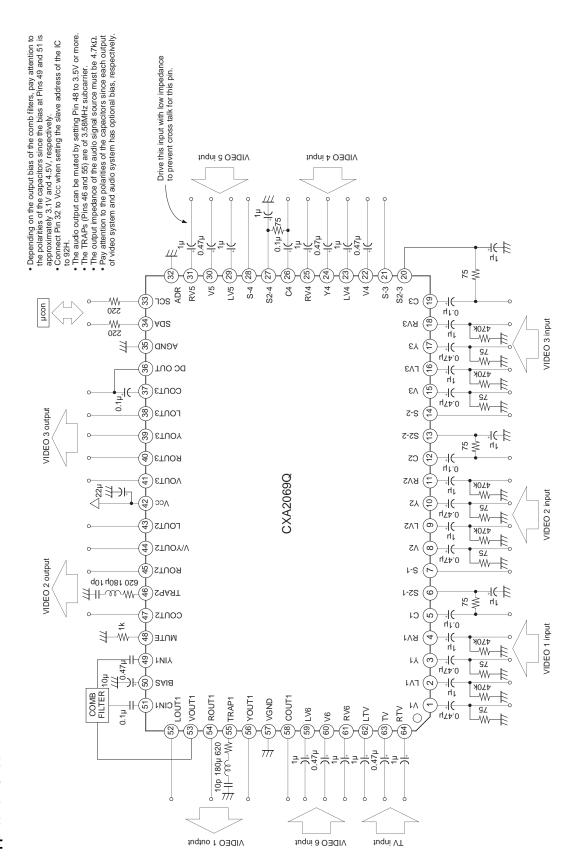

### **Block Diagram**

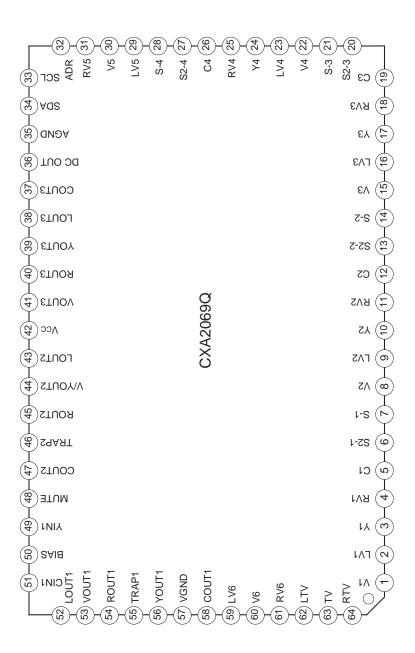

# **Pin Description**

| Pin<br>No.                                                      | Symbol                                                                           | Pin voltage | Equivalent circuit                                                  | Description                                                                                                                              |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------|-------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 63<br>1<br>8<br>15<br>22<br>30<br>60                            | TV<br>V1<br>V2<br>V3<br>V4<br>V5<br>V6                                           | 4.0 V       | 63 22 150 150 WW 3µA 7/77                                           | Video signal inputs. Input composite video signals.                                                                                      |

| 3<br>10<br>17<br>24<br>49                                       | Y1<br>Y2<br>Y3<br>Y4<br>YIN1                                                     | 4.0 V       | 3 Vcc 150 150 49 7/7 3µA 7/77                                       | Y/C separation signal inputs. Input luminance signals. The YIN1 pin inputs the signal obtained by Y/C separating the VOUT1 pin output.   |

| 5<br>12<br>19<br>26<br>51                                       | C1<br>C2<br>C3<br>C4<br>CIN1                                                     | 4.5 V       | 5<br>12<br>20k<br>19<br>150<br>27k ₹<br>7//7                        | Y/C separation signal inputs. Input chrominance signals. The CIN1 pin inputs the signal obtained by Y/C separating the VOUT1 pin output. |

| 62, 2<br>9, 16<br>23, 29<br>59, 64<br>4, 11<br>18, 25<br>31, 61 | LTV, LV1<br>LV2, LV3<br>LV4, LV5<br>LV6, RTV<br>RV1, RV2<br>RV3, RV4<br>RV5, RV6 | 4.5 V       | 62 64<br>2 4<br>9 11<br>16 18<br>23 25<br>29 31<br>59 61 777<br>777 | Audio signal inputs.                                                                                                                     |

| 53<br>41                                                        | VOUT1<br>VOUT3                                                                   | 3.9 V       | Vcc                                                                 | Video signal outputs. Output composite video signals.                                                                                    |

| Pin<br>No.                       | Symbol                                             | Pin voltage | Equivalent circuit                      | Description                                                                                                                                                                                                                                                                                                          |

|----------------------------------|----------------------------------------------------|-------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 44                               | V/YOUT2                                            | 3.8 V       | Vcc Vcc Vcc Vcc 444                     | Video signal output. Either composite video signal output or luminance signal output can be selected by I <sup>2</sup> C bus control.                                                                                                                                                                                |

| 56                               | YOUT1                                              | 3.3 V       | Vcc Vcc Vcc Vcc                         | Video signal outputs. Output luminance signals.                                                                                                                                                                                                                                                                      |

| 39                               | YOUT3                                              | 3.8 V       | 39 777 777 777                          |                                                                                                                                                                                                                                                                                                                      |

| 58<br>47<br>37                   | COUT1<br>COUT2<br>COUT3                            | 4.5 V       | Vcc | Video signal outputs. Output chrominance signals.                                                                                                                                                                                                                                                                    |

| 52<br>43<br>38<br>54<br>45<br>40 | LOUT1<br>LOUT2<br>LOUT3<br>ROUT1<br>ROUT2<br>ROUT3 | 4.5V        | 54 52                                   | Audio signal outputs. Zo=50 $\Omega$ (within DC ±2 mA)                                                                                                                                                                                                                                                               |

| 6<br>13<br>20<br>27              | \$2-1<br>\$2-2<br>\$2-3<br>\$2-4                   | _           | 6 Vcc Vcc Vcc 13 147 100k               | Detects the S2-compatible DC superimposed onto the C signal. 4: 3 video signal at 1.3 V or less 4: 3 letter-box signal at 1.3 V or more to 2.5 V or less 16: 9 picture squeezed signal at 2.5 V or more This pin is pulled down to GND by a 100 k $\Omega$ resistor, so the 4: 3 video signal is selected when open. |

| Pin<br>No.          | Symbol                   | Pin voltage | Equivalent circuit                       | Description                                                                                                                                                                                                                                                             |

|---------------------|--------------------------|-------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>14<br>21<br>28 | S-1<br>S-2<br>S-3<br>S-4 | _           | 7 Vcc Vcc Vcc Vcc Vcc Vcc Vcc Vcc Vcc Vc | Composite video/S selector. The detection results are written to the status register. S signal at 3.5 V or less Composite video signal at 3.5 V or more This pin is pulled up to 5 V by a 100 k $\Omega$ resistor, so the composite video signal is selected when open. |

| 32                  | ADR                      | _           | Vcc<br>147 72k<br>32                     | Selects the slave address<br>for the I <sup>2</sup> C bus.<br>90H at 1.5 V or less<br>92H at 2.5 V or more<br>90H when open.                                                                                                                                            |

| 33                  | SCL                      | _           | 33                                       | I <sup>2</sup> C bus signal input<br>Vı∟max=1.5 V<br>Vıнmin=3.0 V                                                                                                                                                                                                       |

| 34                  | SDA                      | _           | 4k Vcc                                   | I <sup>2</sup> C bus signal input<br>Vı∟max=1.5 V<br>Vıнmin=3.0 V<br>Vo∟max=0.4 V                                                                                                                                                                                       |

| Pin<br>No. | Symbol         | Pin voltage | Equivalent circuit                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|----------------|-------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36         | DC_OUT         | _           | Vcc<br>4k 1k Q1<br>28k ₹ 7/17           | Outputs the S2-compatible DC superimposed onto the COUT3 output. The DC is superimposed by connecting this pin to the COUT3 output via a capacitor. Control is performed by the I²C bus. When 0 V is output, Q1 is ON and the impedance is $5 \text{ k}\Omega$ . S2 protocol output impedance of $10 \pm 3 \text{ k}\Omega$ is realized by attaching external resistance of $4.7 \text{ k}\Omega$ . DC_OUT (bus) Output DC 0 4.5 V 1 0 V 2 1.9 V 3 4.5 V |

| 55<br>46   | TRAP1<br>TRAP2 | 3.8 V       | Vcc  100  1k \$  7/77                   | Connects trap circuit for subcarrier.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 48         | MUTE           | _           | Vcc<br>147 72k<br>48                    | Audio signal output mute.  Mute OFF at 1.5 V or less  Mute ON at 2.5 V or more  Mute OFF when open.                                                                                                                                                                                                                                                                                                                                                      |

| 50         | BIAS           | 4.5 V       | Vcc | Internal reference bias (Vcc/2). Connect to GND via a capacitor.                                                                                                                                                                                                                                                                                                                                                                                         |

### **Electrical Characteristics**

(Ta=25 °C Vcc=9 V)

| Item                | Symbol | Conditions         | Min. | Тур. | Max. | Unit |

|---------------------|--------|--------------------|------|------|------|------|

| Current consumption | Icc    | No signal, no load | 40   | 55   | 72   | mA   |

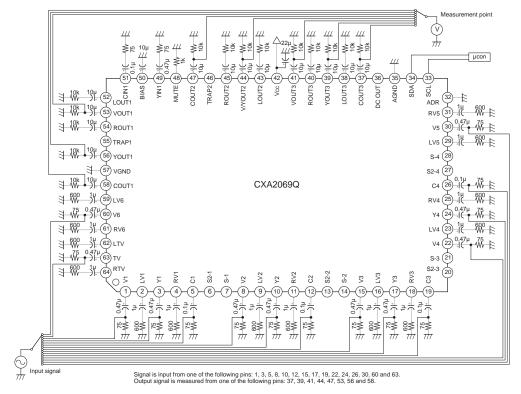

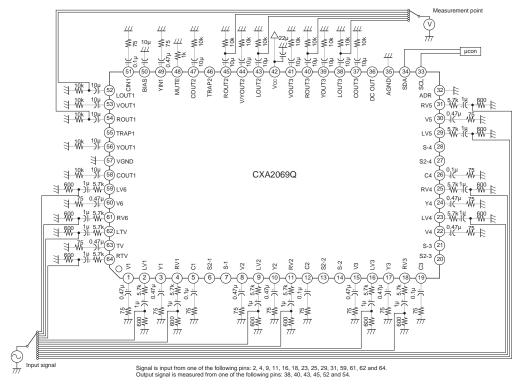

# Video system (Measurement circuit; Fig. 1)

| Gain                                         | GVv   | f=100 kHz, 0.3 Vp-p input                                                       | 5.9 | 6.4 | 6.9 | dB   |

|----------------------------------------------|-------|---------------------------------------------------------------------------------|-----|-----|-----|------|

| Frequency response characteristics           | FBWv1 | f=100 kHz, input frequency where output amplitude is –3 dB with 0.3 Vp-p output | 15  | 20  |     | MHz  |

| Frequency response characteristics (Y/C mix) | FBWv2 | serving as 0 dB                                                                 | 10  | 15  | _   | MHz  |

| Input dynamic range                          | Ddv   | f=100 kHz, maximum with distortion < 1.0 %                                      | 1.4 | _   | _   | Vp-p |

| Cross talk                                   | Vctv  | f=4.43 MHz, 1 Vp-p input                                                        | _   | _   | -50 | dB   |

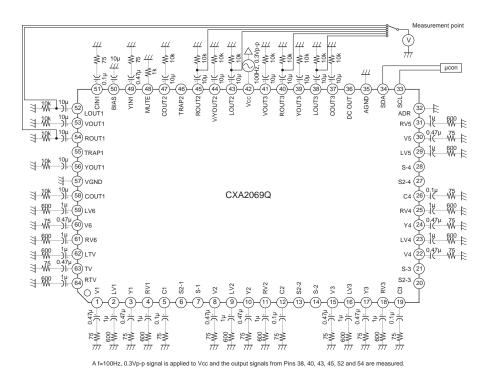

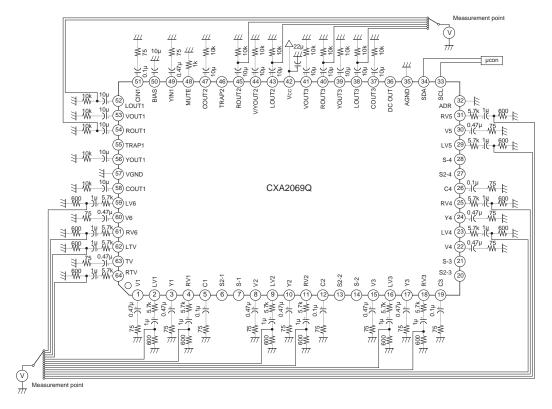

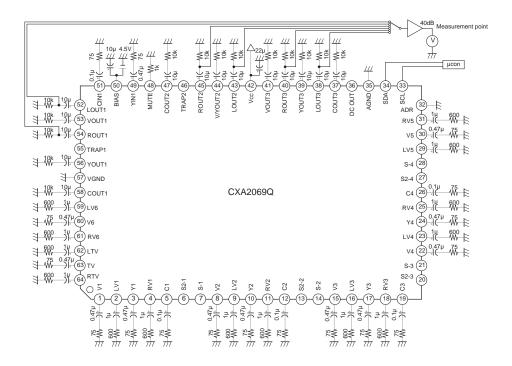

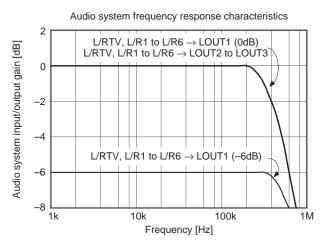

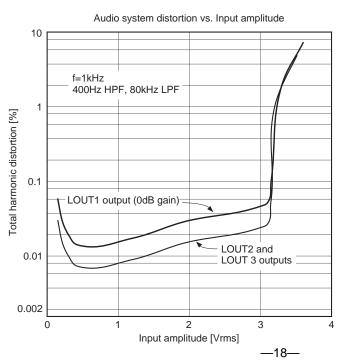

# Audio system (Measurement circuits; Fig. 2 to Fig. 5)

| Gain                                                       | GVA  | f=1 kHz, 1 Vp-p input, 5.7 kΩ                                                                                                                                                                                                                                        | -1  | 0           | 1    | dB    |

|------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|------|-------|

| Frequency response characteristics                         | FBWa | resistor inserted to input  f=1 kHz, input frequency where output amplitude is -3 dB with 1 Vp-p output serving as 0 dB  f=1 kHz, 2.2 Vp-p input, where 400 Hz HPF+80 kHz LPF are inserted  Dda f=1 kHz, maximum with distortion < 0.3 %  Vcta f=1 kHz, 1 Vp-p input |     | _           |      | kHz   |

| Total harmonic distortion                                  | THD  |                                                                                                                                                                                                                                                                      | _   | 0.03        | 0.05 | %     |

| Input dynamic range                                        | Dda  | f=1 kHz, maximum with distortion < 0.3 %                                                                                                                                                                                                                             | 2.8 | 3.0         | l    | Vrms  |

| Cross talk                                                 | VctA | f=1 kHz, 1 Vp-p input                                                                                                                                                                                                                                                | _   | -90         | -80  | dB    |

| Ripple rejection ratio                                     | VctA | f=100 Hz, 0.3 Vp-p applied to Vcc                                                                                                                                                                                                                                    | _   | <b>–</b> 55 | -40  | dB    |

| Output DC offset                                           | Voff | Offset voltage between input and output                                                                                                                                                                                                                              | -30 | _           | 30   | mV    |

| Residual noise VNA When 400 Hz HPF+30 kHz LPF are inserted |      |                                                                                                                                                                                                                                                                      | 0   | 20          | 30   | μVrms |

| S/N ratio                                                  | S/N  | f=1 kHz, 1 Vrms input<br>fcL=400 Hz, fcH=30kHz                                                                                                                                                                                                                       |     | -100        | -90  | dB    |

# Logic system

| Item                                         | Symbol  | Conditions                     | Min. | Тур. | Max. | Unit |

|----------------------------------------------|---------|--------------------------------|------|------|------|------|

| High level input voltage                     | ViH     |                                | 3.0  | _    | 5.0  | V    |

| Low level input voltage                      | VIL     |                                | 0    | _    | 1.5  | V    |

| Low level output voltage                     | Vol     | With SDA 3 mA current supplied | 0    | _    | 0.4  | V    |

| High level input current                     | Іін     | V <sub>I</sub> H=4.5V          | 0    | _    | 10   | μA   |

| Low level input current                      | lı∟     | VIL=0.4V                       | 0    | _    | 10   | μA   |

| Maximum clock frequency                      | fscL    |                                | 0    | _    | 100  | kHz  |

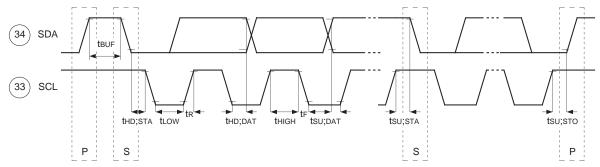

| Minimum waiting time for data change         | tBUF    |                                | 4.7  | _    | _    | μs   |

| Minimum waiting time for data transfer start | thd;sta |                                | 4.0  | _    | _    | μs   |

| Low level clock pulse width                  | tLOW    |                                | 4.7  | _    | _    | μs   |

| High level clock pulse width                 | tніgн   |                                | 4.0  | _    | _    | μs   |

| Minimum waiting time for start preparation   | tsu;sta |                                | 4.7  | _    | _    | μs   |

| Minimum data hold time                       | thd;dat |                                | 300  | _    | _    | ns   |

| Minimum data preparation time                | tsu;dat |                                | 250  | _    | _    | ns   |

| Rise time                                    | tr      |                                | _    | _    | 1    | μs   |

| Fall time                                    | tF      |                                | _    | _    | 300  | ns   |

| Minimum waiting time for stop preparation    | tsu;sto |                                | 4.7  | _    | _    | μs   |

Fig. 1 Video system (gain, frequency response characteristics, input dynamic range, cross talk) measurement circuit

Fig. 2 Audio system (gain, frequency response characteristics, total harmonic distortion, input dynamic range, cross talk) measurement circuit

Fig. 3 Audio system (ripple rejection ratio) measurement circuit

Fig. 4 Audio system (output DC offset voltage) measurement circuit

Fig. 5 Audio system (residual noise) measurement circuit

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

#### I<sup>2</sup>C BUS Control Signal

Fig. 6 I2C BUS Control Signal Timing Chart

#### **Description of Operation**

The CXA2069Q is a TV I<sup>2</sup>C bus-compatible AV switch IC. The video system and the stereo audio system both have 7 inputs and 3 outputs each. 4 of the 7 video system inputs support S2 and S protocols.

The desired inputs can be independently assigned to each output (in the audio system, the left and right channels are processed as one unit) by I<sup>2</sup>C bus control. However, the same input is assigned to both the video and audio system output 3.

#### I<sup>2</sup>C BUS Registers

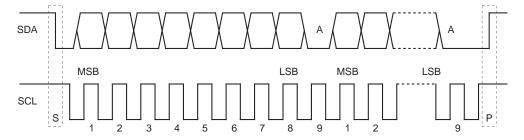

#### 1) I2C BUS

The I<sup>2</sup>C bus (inter-IC bus) is an inter-IC bus system developed by Philips. Two lines (SDA–serial data, SCL–serial clock) provide control over start, stop, data transfer, synchronization, and collision avoidance. The IC outputs are either open collector or open drain, forming a bus line in the wired OR format.

S: Start condition; SDA is set "Low" when SCL is "High"

P: Stop condition; SDA is set "High" when SCL is "High"

A: Acknowledge; signal sent from the slave

Data is transmitted by MSB-first. One data unit consists of 8 bits, to which the acknowledge signal, which indicates that the data has been accepted by the slave, is attached at the end. Normally, the slave\*1 IC receives data at the rising edge of SCL and the master\*2 IC changes data at the falling edge of SCL.

\*1 Slave : An IC that is placed under the control of the master.

In a normal system, all devices excluding the central microcomputer are slaves.

\*2 Master: A central microcomputer or other controlling IC.

#### 2) Control Registers

The CXA2069Q control is exercised by writing 3-byte data into the three 8-bit control registers which control the output selector circuits for the 3 outputs.

| S | Slave address | Α | DATA1 | Α | DATA2 | Α | DATA3 | Α | Р |

|---|---------------|---|-------|---|-------|---|-------|---|---|

|---|---------------|---|-------|---|-------|---|-------|---|---|

S; Start conditionA; AcknowledgeP; Stop condition

O Control register structure (DATA1 to DATA3)

• All registers are set to "0" during IC power on.

• "\*" indicates undefined.

|            | b7     | b6      | b5          | b4     | b3 | b2 | b1     | b0  |

|------------|--------|---------|-------------|--------|----|----|--------|-----|

| Slave add. | 1      | 0       | 0           | 1      | 0  | 0  | ADR    | R/W |

| DATA1      | A-GAIN | S/COMP1 | V-IN1 A-IN1 |        |    |    |        |     |

| DATA2      | V/YOUT | S/COMP2 | V-IN2       |        |    |    | A-IN2  |     |

| DATA3      | *      | S/COMP3 |             | AV-IN3 |    |    | DC OUT | *   |

R/W (1): Read/write mode

0 : Control data write

1: Status register read

ADR (1): This bit sets the slave address set by the address pin.

0:90H 1:92H

A-GAIN (1): LOUT1/ROUT1 output gain selector

0: 0 dB output 1: -6 dB output

S/COMP1 to S/COMP3 (1 each): S terminal input/composite signal input selectors

By setting S/COMP1 to "0", when composite signal input is selected, YOUT1/COUT1 output the inputs from YIN1/CIN1 during video 1 output.

0 : Composite signal inputs (TV, V1 to V6 inputs)

1 : S terminal inputs (Y1/C1 to Y4/C4 inputs)

V/YOUT (1): This bit selects the output to Pin 44 (V/YOUT2).

0: VOUT (composite signal) output

1 : YOUT (luminance signal) output

V-IN1 to V-IN2 (3 each): These bits select the input signals output to each video output.

V-IN1 corresponds to the VOUT1 and YOUT1/COUT1 outputs, and V-IN2 to the VOUT2 and YOUT2/COUT2 outputs.

0 : Mute 4 : Selects the V3 and Y3/C3 inputs

1 : Selects the TV input 5 : Selects the V4 and Y4/C4 inputs

2 : Selects the V1 and Y1/C1 inputs3 : Selects the V2 and Y2/C2 inputs6 : Selects the V5 input7 : Selects the V6 input

A-IN1 to A-IN2 (3 each): These bits select the input signals output to each audio output.

A-IN1 corresponds to the LOUT1/ROUT1 outputs, and A-IN2 to the LOUT2/ROUT2 outputs.

0 : Mute 4 : Selects the LV3/RV3 inputs

1 : Selects the LTV/RTV inputs

2 : Selects the LV1/RV1 inputs

5 : Selects the LV4/RV4 inputs

6 : Selects the LV5/RV5 inputs

3 : Selects the LV2/RV2 inputs 7 : Selects the LV6/RV6 inputs

AV-IN3 (3): This bit selects the input signals output to output 3.

Both the video output and the audio output are selected at the same time only for AV-IN3.

0 : Mute 4 : Selects the V3, Y3/C3 and LV3/RV3 inputs

1 : Selects the TV and LTV/RTV inputs 5 : Selects the V4, Y4/C4 and LV4/RV4 inputs

2 : Selects the V1, Y1/C1 and LV1/RV1 inputs 6 : Selects the V5 and LV5/RV5 inputs

3 : Selects the V2, Y2/C2 and LV2/RV2 inputs 7 : Selects the V6 and LV6/RV6 inputs

DC OUT (2): These bits set the DC voltage output from Pin 35 (DC OUT).

0:4.5 V

1:0 V

2:1.9 V

3:4.5 V

#### 3) Status Registers

• When reading two bytes

| S | Slave address | Α | DATA1 | Α | DATA2 | NA | Р |

|---|---------------|---|-------|---|-------|----|---|

• When reading one byte

| S Slave address A DATA1 NA | S | Slave address | Α | DATA1 | NA | Р |

|----------------------------|---|---------------|---|-------|----|---|

|----------------------------|---|---------------|---|-------|----|---|

S; Start condition

A; Acknowledge

NA; No acknowledge

P; Stop condition

When communication is to be terminated in the status register reading mode, the "no-acknowledge" signal is needed to assure that the master does not issue the acknowledge signal to the slave.

It is possible to read only DATA1 of the status register by sending the no-acknowledge signal after DATA1.

#### O Status register structure (DATA1 to DATA2)

|            | b/    | b6    | b5    | b4    | b3        | b2 | b1  | bO |

|------------|-------|-------|-------|-------|-----------|----|-----|----|

| Slave add. | 1     | 0     | 0     | 1     | 0         | 0  | ADR | 1  |

| DATA1      | S1SEL | S2SEL | S3SEL | S4SEL | S-        | C1 | S-  | C2 |

| DATA2      | S1SEL | S2SEL | S3SEL | S4SEL | S-C3 S-C4 |    | C4  |    |

S1SEL to S4SEL (1 each): S-1 to S-4 pin status

0; S-1 to S-4 pins are not grounded.

1; S-1 to S-4 pins are grounded.

S1SEL to S4SEL are actually determined by comparing the S-1 to S-4 pin DC voltages with 3.5 V.

| S-1 to S-4 pin DC voltage | S1SEL to S4SEL |

|---------------------------|----------------|

| 3.5 V or more             | 0              |

| 3.5 V or less             | 1              |

S-C1, S-C2, S-C3, S-C4 (2 each): S2-1, S2-2, S2-3 and S2-4 pin status

0; 4: 3 video signal

1; 4: 3 letter-box signal

2; 16: 9 video squeezed signal

3; No signal

S-C1 to S-C4 are actually determined by comparing the S2-1 to S2-4 pin DC voltages with two threshold. However, when the S-1 to S-4 pins are open, the outputs are fixed to "3".

| S2-1 to S2-4 pin DC voltage    | S-C1 to S-C4 |  |  |

|--------------------------------|--------------|--|--|

| 1.3 V or less                  | 0            |  |  |

| 1.3 V or more to 2.5 V or less | 1            |  |  |

| 2.5 V or more                  | 2            |  |  |

| S-1 to S-4 OPEN                | 3            |  |  |

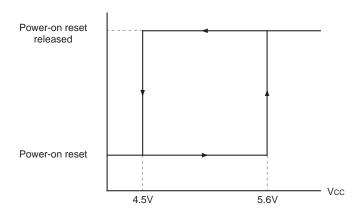

#### 4) Power-on Reset

The CXA2069Q has an internal power-on reset function that sets each control register to "0" during IC power ON.

The power-on reset V<sub>TH</sub> has hysteresis.

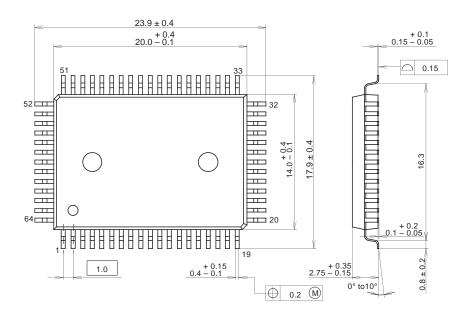

# Package Outline Unit: mm

### 64PIN QFP(PLASTIC)

### PACKAGE STRUCTURE

| SONY CODE  | QFP-64P-L01   |

|------------|---------------|

| EIAJ CODE  | QFP064-P-1420 |

| JEDEC CODE |               |

| PACKAGE MATERIAL | EPOXY RESIN                 |

|------------------|-----------------------------|

| LEAD TREATMENT   | SOLDER/PALLADIUM<br>PLATING |

| LEAD MATERIAL    | 42/COPPER ALLOY             |

| PACKAGE MASS     | 1.5g                        |